This product has no reviews yet.

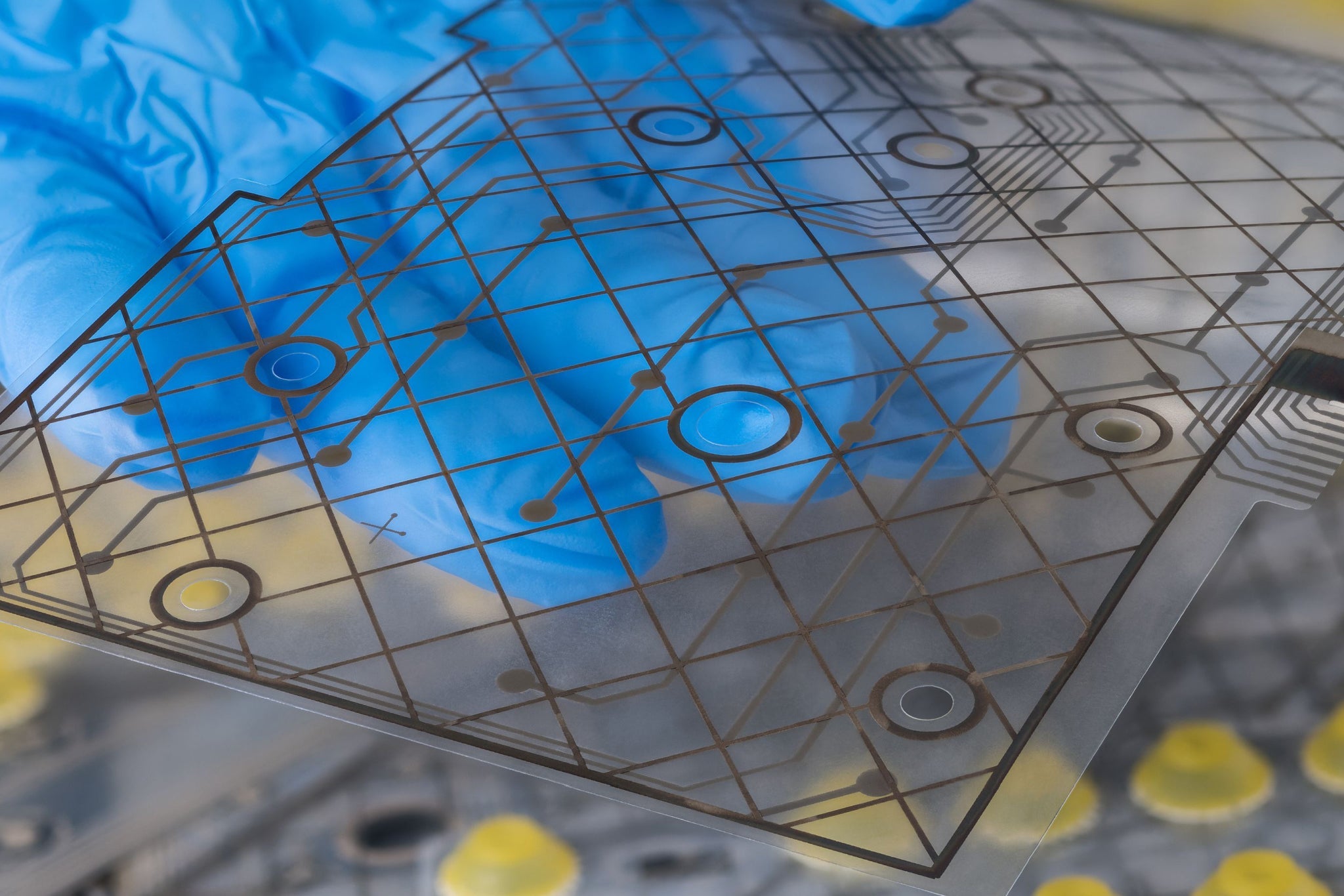

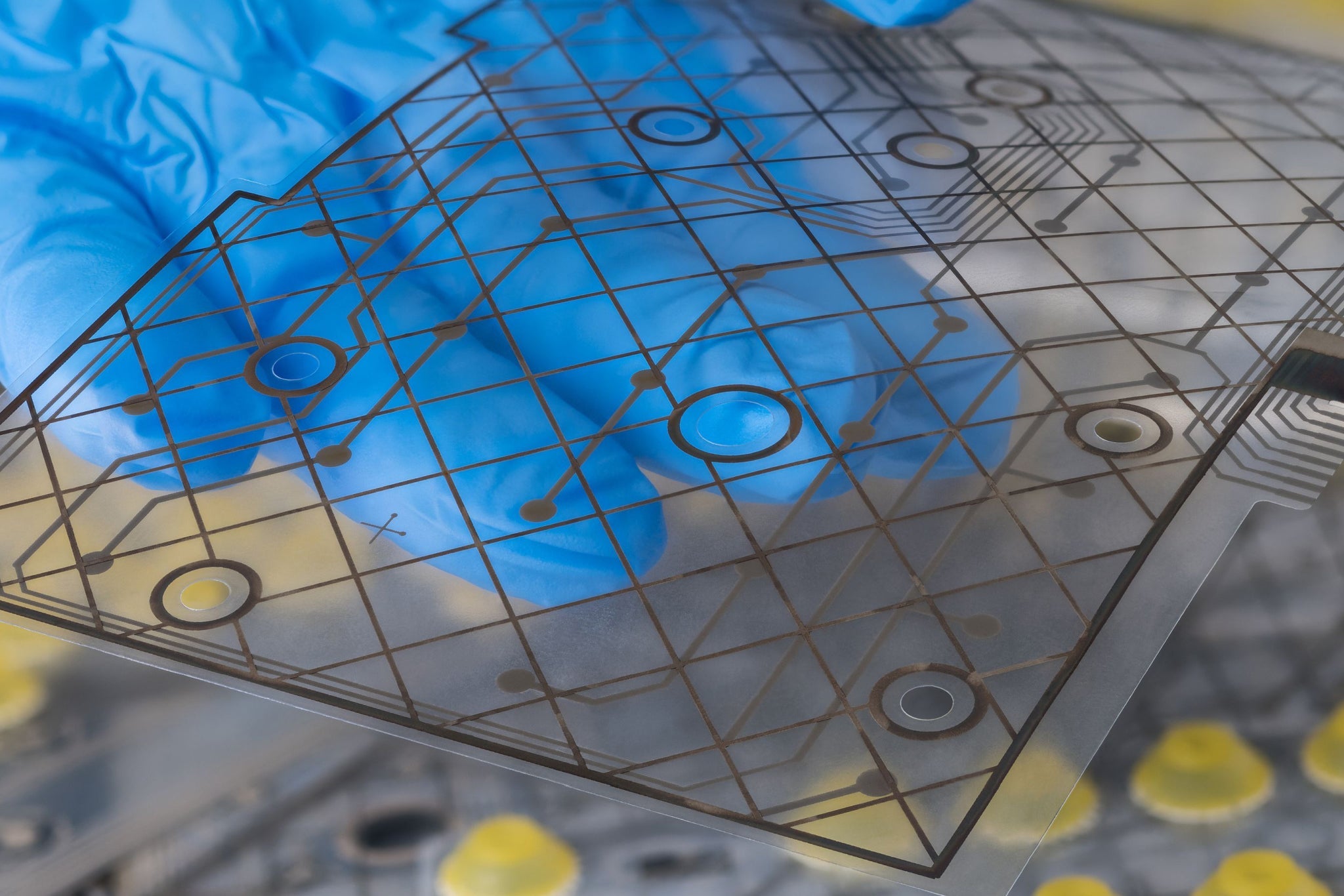

SEMI106 Flexible Hybrid Electronics 2.0 based on Fan-Out Wafer Packaging

Learn why and how new packaging paradigms like chiplets and dielets are impacting the world of flexible hybrid electronics (FHE) from one of the industry's foremost experts, Dr. Subramanian Iyer of UCLA. The course explores how these packages are packing such a punch and enabling advanced performance in a much smaller and flexible footprint.

Overview: In the last few years, electronics packaging has rightfully emerged from the shadows of CMOS scaling to make a significant impact in high performance and mobile appliance computing.

The area of Flexible Hybrid Electronics (FHE) has also developed and is making a significant impact in the area of medical and wellness electronics. The first generation of these devices have, for most part, adapted Printed Circuit Board (PCB) technology by using thinner PCBs and assembling either thinned or thin packaged “older” generation of chips on to these platforms, typically with coarse printed wiring to connect a small number of such chips.

This approach, while immensely useful to get the field going, needs to adapt and borrow from the both silicon and advanced packaging technology trends, so that we can advance this trend to the next level. The key paradigm challenges ahead are: scaling FHE in general – this includes the adoption of dielet (chiplet) technology in more advanced CMOS nodes including edge-AI, higher performance interconnects, flexible high-density energy storage, wireless communication and advanced ergonomics and all of these at lower cost and higher reliability.

This talk addresses the challenges and outline a possible technology roadmap to achieve these goals in the next few years.

About Professor Iyer: Subramanian S. Iyer (Subu) is Distinguished Professor at the University of California at Los Angeles. He is Director of the Center for Heterogeneous Integration and Performance Scaling (CHIPS). Prior to that he was an IBM Fellow. His key technical contributions have been the development of the world’s first SiGe base HBT, Salicide, electrical fuses, embedded DRAM and 45nm technology node used to make the first generation of truly low power portable devices as well as the first commercial interposer and 3D integrated products. He has been exploring new packaging paradigms and device innovations that they may enable wafer-scale architectures, in-memory analog compute and medical engineering applications.

Overview: In the last few years, electronics packaging has rightfully emerged from the shadows of CMOS scaling to make a significant impact in high performance and mobile appliance computing.

The area of Flexible Hybrid Electronics (FHE) has also developed and is making a significant impact in the area of medical and wellness electronics. The first generation of these devices have, for most part, adapted Printed Circuit Board (PCB) technology by using thinner PCBs and assembling either thinned or thin packaged “older” generation of chips on to these platforms, typically with coarse printed wiring to connect a small number of such chips.

This approach, while immensely useful to get the field going, needs to adapt and borrow from the both silicon and advanced packaging technology trends, so that we can advance this trend to the next level. The key paradigm challenges ahead are: scaling FHE in general – this includes the adoption of dielet (chiplet) technology in more advanced CMOS nodes including edge-AI, higher performance interconnects, flexible high-density energy storage, wireless communication and advanced ergonomics and all of these at lower cost and higher reliability.

This talk addresses the challenges and outline a possible technology roadmap to achieve these goals in the next few years.

About Professor Iyer: Subramanian S. Iyer (Subu) is Distinguished Professor at the University of California at Los Angeles. He is Director of the Center for Heterogeneous Integration and Performance Scaling (CHIPS). Prior to that he was an IBM Fellow. His key technical contributions have been the development of the world’s first SiGe base HBT, Salicide, electrical fuses, embedded DRAM and 45nm technology node used to make the first generation of truly low power portable devices as well as the first commercial interposer and 3D integrated products. He has been exploring new packaging paradigms and device innovations that they may enable wafer-scale architectures, in-memory analog compute and medical engineering applications.

SEMI106 Flexible Hybrid Electronics 2.0 based on Fan-Out Wafer Packaging

Sale price$99.00 USD

Regular price$99.00 USD (/)

This product has no reviews yet.